CH224D - USB Power Delivery Controller (v1.0 Only)

USB Power Delivery protocol negotiation IC for obtaining 15V/3A power from USB-C PD chargers.

CH224D is used in v1.0 only and has been replaced by STUSB4500 in v1.1.

Reason for replacement: CH224D has poor charger compatibility (~33%). Only 2 out of 6 tested USB-PD chargers worked with CH224D. STUSB4500 is USB-IF certified with ~95%+ expected compatibility.

| Charger | CH224D (v1.0) | STUSB4500 (v1.1) |

|---|---|---|

| Anker Nano II 65W | ✅ Works | ✅ Expected |

| Anker Prime 200W | ❌ Fails | ✅ Expected |

| Elecom EC-AC67150BK | ❌ Fails | ✅ Expected |

| Digiforce Square 65W | ❌ Fails | ✅ Expected |

| CIO NovaPort SLIM 45W | ❌ Fails | ✅ Expected |

See GitHub Issue #33 for details.

CH224D does NOT have a separate VOUT pin!

- Pin 2 (VBUS) is BOTH input (initially 5V) AND output (15V after PD negotiation)

- Pin 18 is NC (Not Connected) - no separate output pin exists

- Voltage changes from 5V → 15V on the same VBUS pin after PD negotiation

- Downstream circuits connect directly to VBUS

For 15V configuration:

- Rset = 56 KΩ resistor from DRV/CFG1 junction to GND

- Pin 1 (DRV) and Pin 19 (CFG1) connected together, then through Rset to GND

- CC pull-downs required: 5.1kΩ resistors on CC1 and CC2 to GND (identifies device as USB-PD sink)

See datasheet page 4 (Section 6.1) for reference schematic.

Overview

The CH224D is a USB Power Delivery (PD) protocol controller IC manufactured by WCH (Nanjing Qinheng Microelectronics). In this project, it communicates with USB-C PD chargers to negotiate 15V output, which serves as the input voltage for the modular synthesizer power supply.

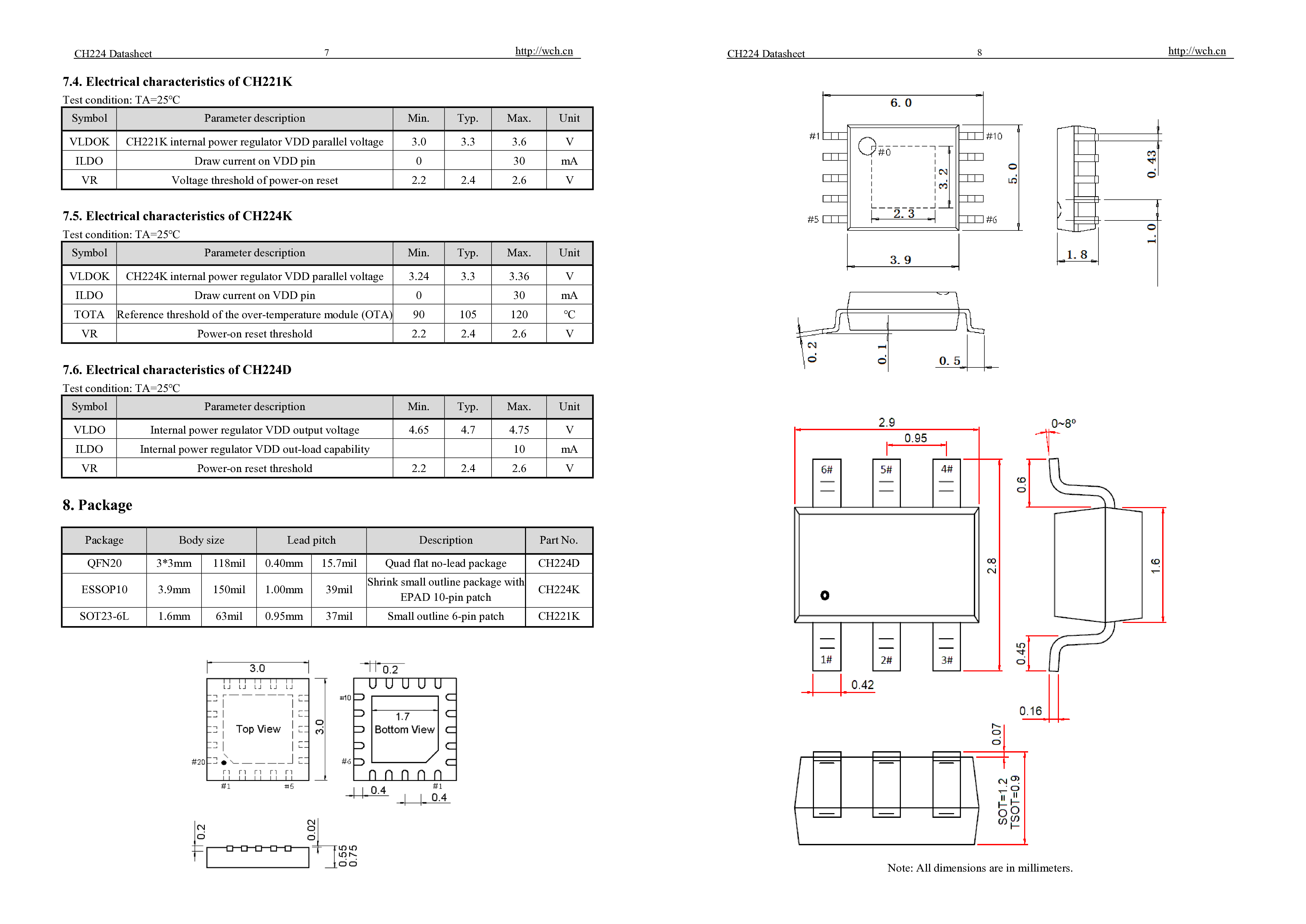

Through CFG pin configuration, it can select PD voltage profiles of 5V/9V/12V/15V/20V without requiring an external microcontroller. The compact QFN-20 package minimizes PCB footprint while achieving low cost and high reliability.

Key Specifications

| Parameter | Value | Notes |

|---|---|---|

| JLCPCB Part Number | C3975094 | |

| Manufacturer Part Number | CH224D | |

| Package | QFN-20 (3mm × 3mm) | Surface-mount |

| Stock Availability | 2,291 units | Good availability |

| Unit Price | $0.36 | JLCPCB pricing |

| Input Voltage Range | 4V - 22V DC | From USB-C VBUS |

| Output Voltage Options | 5V / 9V / 12V / 15V / 20V | PD negotiated |

| Maximum Current | 3A | Depends on PD source capability |

| PD Protocol Support | USB PD 2.0 / 3.0 | |

| Configuration Method | Resistor-based CFG pins | No MCU required |

| Operating Temperature | -40°C to +100°C |

Pin Configuration

CH224D (QFN-20)

Top View

┌─────────────────────────┐

│ │

DRV │1 20│ (Reserved)

VBUS│2 19│ CFG1

│3 18│ NC (Not Connected)

│4 17│ (Reserved)

GATE│5 16│ (Reserved)

│ │

NMOS#│6 15│ ISN

VDD │7 14│ ISP

DP │8 13│ CFG2

DM │9 12│ CFG3

CC2 │10 11│ CC1

│ ┌──────────┐ │

└────┤ Exposed ├────────┘

│ Pad (0) │

│ GND │

└──────────┘

**CRITICAL**: Pin 11 = CC1, Pin 10 = CC2 (not the other way around!)

Note: QFN-20 numbering goes counter-clockwise from pin 1. Pin 0 refers to the exposed pad (EPAD) which must be connected to GND for thermal dissipation.

Pin Descriptions

| Pin | Name | Function | Connection in Design |

|---|---|---|---|

| 0 (EPAD) | GND | Ground / Thermal pad | System ground plane |

| 1 | DRV | Weak driving output for configuration resistor | Connected to CFG1 (pin 19), then through Rset (56kΩ) to GND |

| 2 | VBUS | Power I/O (input 5V → output 15V after PD) | USB-C connector VBUS (initially 5V, becomes 15V after negotiation) |

| 5 | GATE | Internal NMOS gate driver | Internal connection only (no external connection) |

| 6 | NMOS# | External NMOS control | Tied to GND (enables internal switch mode) |

| 7 | VDD | Internal voltage regulator output (4.7V) | 1µF decoupling capacitor to GND |

| 8 | DP | USB D+ data line (UDP) | Shorted to pin 9 (DM) for PD-only mode |

| 9 | DM | USB D- data line (UDM) | Shorted to pin 8 (DP) for PD-only mode |

| 10 | CC2 | USB Type-C Configuration Channel 2 | USB-C connector CC2 + 5.1kΩ pull-down to GND |

| 11 | CC1 | USB Type-C Configuration Channel 1 | USB-C connector CC1 + 5.1kΩ pull-down to GND |

| 12 | CFG3 | Voltage configuration pin 3 (digital input) | Open (no connection) |

| 13 | CFG2 | Voltage configuration pin 2 (digital input) | Open (no connection) |

| 14 | ISP | Current sense positive | Shorted to pin 15 (ISN), then to GND (not using current sensing) |

| 15 | ISN | Current sense negative | Shorted to pin 14 (ISP), then to GND (not using current sensing) |

| 18 | NC | Not Connected (no separate output pin!) | No connection - VBUS (pin 2) is the output! |

| 19 | CFG1 | Voltage configuration pin 1 (analog input) | Connected to DRV (pin 1), then through Rset (56kΩ) to GND |

Voltage Configuration - Resistance Mode

The CH224D supports two configuration modes. This design uses Resistance Configuration Mode (simpler, no MCU needed).

Resistance Configuration Mode (Recommended)

Circuit Topology:

DRV (Pin 1) ──┬── CFG1 (Pin 19) ← These pins connected together

│

R11 (Rset = 56kΩ, 0603, ±0.1%)

│

GND

CFG2 (Pin 13) ─── Open (or GND)

CFG3 (Pin 12) ─── Open (or GND)

How it works:

1. DRV pin provides weak drive output

2. Resistor value determines voltage at CFG1

3. CH224D reads CFG1 voltage to determine requested voltage

Resistor Values (Rset):

| Rset Value | Requested Voltage |

|---|---|

| 6.8 KΩ | 9V |

| 24 KΩ | 12V |

| 56 KΩ | 15V ✅ This design |

| NC (Not Connected) | 20V |

This Design Configuration:

- Rset = 56 KΩ from DRV/CFG1 junction to GND

- DRV (Pin 1) connects to CFG1 (Pin 19)

- CFG1 and DRV junction connects through Rset (56kΩ) to GND

- CFG2 = Open (or GND)

- CFG3 = Open (or GND)

- Result: CH224D negotiates 15V from PD adapter

Application Circuit

USB-C Connector (6-pin):

┌─────────────────────────────┐

│ 2, 5 VBUS ───────────────┼──→ VBUS Rail (5V initially, 15V after PD)

│ │

│ 3 CC1 ───────────────┼──→ To CH224D CC1

│ 4 CC2 ───────────────┼──→ To CH224D CC2

│ │

│ 1, 6 GND ───────────────┼──→ System GND

└─────────────────────────────┘

CH224D IC (QFN-20) - USB PD Sink Controller:

┌──────────────────────────────┐

VBUS (5V→15V) ──────┤ 2. VBUS (Power I/O) │

│ │

┌──┤11. CC1 (PD Comm) │──→ To USB-C CC1

│ │10. CC2 (PD Comm) │──→ To USB-C CC2

│ │ │

│ │ 1. DRV ──┬──────────────────│

│ │19. CFG1 ──┘ │

│ │13. CFG2 ── Open │

│ │12. CFG3 ── Open │

│ │ │

│ │ 8. DP ──┬──────────────────│ ← SHORT together

│ │ 9. DM ──┘ │ ← (PD-only mode)

│ │ │

│ │ 7. VDD (4.7V LDO) │──→ C30 (1µF) ──→ GND

│ │ │

│ │ 5. GATE (Internal Switch) │ ── NC (internal use only)

│ │ 6. NMOS# (Ext Switch Ctrl) │──→ GND (not using ext)

│ │ │

│ │14. ISP (Current Sense +) ──┬─│

│ │15. ISN (Current Sense -) ──┘ │──→ GND (not using)

│ │ │

│ │18. NC (Not Connected) │──→ No connection

│ │ │

GND │ 0. GND (EPAD) │

└──────────────────────────────┘

CRITICAL: VBUS is both input AND output!

- Initially: VBUS = 5V (default USB)

- After PD negotiation: VBUS = 15V (requested voltage)

- Pin 18 is NC - NO separate output pin!

- Downstream circuits connect directly to VBUS

Input Filter Capacitors (on VBUS rail):

J1 VBUS ──┬────────────────┬─── CH224D pin 2 (VBUS) ──→ +15VOUT (to DC-DC stages)

│ │

C1 C2

10µF 100nF

electrolytic ceramic

(farther) (CLOSE!)

│ │

GND GND

VDD Decoupling (Internal 4.7V Regulator):

VDD (pin 7) ─── C30 (1µF) ──→ GND (Close to IC)

CC Pin Pull-down Resistors (USB-PD Sink Identification):

CC1 (pin 11) ───┬─── R12 (5.1kΩ) ──→ GND

│

└──→ To USB-C CC1 (pin 3)

CC2 (pin 10) ───┬─── R13 (5.1kΩ) ──→ GND

│

└──→ To USB-C CC2 (pin 4)

Note: 5.1kΩ pull-downs identify device as USB-PD sink (power consumer)

Voltage Configuration (15V Selection via Rset):

DRV (pin 1) ──┬── CFG1 (pin 19) ← These pins connected together

│

R11 (Rset = 56kΩ, 0603, ±0.1%)

│

GND

Connection List

Power Rail (VBUS):

USB-C VBUS (pins 2, 5)→CH224D pin 2 (VBUS)→VBUS Rail- Initially: VBUS = 5V (default USB voltage)

- After PD negotiation: VBUS = 15V (requested voltage)

- This SAME pin serves as power output to DC-DC converters

CC Communication Lines (USB-PD Protocol):

USB-C CC1 (pin 3)→CH224D pin 11 (CC1)→R12 (5.1kΩ)→GNDUSB-C CC2 (pin 4)→CH224D pin 10 (CC2)→R13 (5.1kΩ)→GND- Critical: 5.1kΩ pull-downs (Rd) identify device as USB-PD sink

Ground:

USB-C GND (pins 1, 6)→System GND→CH224D pin 0 (EPAD)(thermal pad)

Input Filter Capacitors:

C1 (10µF/25V electrolytic):VBUS⟷GND(bulk filtering)C2 (100nF ceramic):VBUS⟷GND(high-freq decoupling, close to IC)

VDD Decoupling (Internal 4.7V Regulator):

C30 (1µF ceramic):VDD (pin 7)⟷GND(internal regulator output)

Voltage Configuration (15V Selection):

CH224D pin 1 (DRV)→ Connected topin 19 (CFG1)CFG1→R11 (56kΩ, ±0.1%)→GNDCH224D pin 13 (CFG2)→OpenorGNDCH224D pin 12 (CFG3)→OpenorGND

PD-Only Mode Configuration:

CH224D pin 8 (DP)↔pin 9 (DM)- Shorted together (disables BC1.2 and other USB data protocols)- Why short DP to DM? 6-pin USB-C connector has no DP/DM pins. Per datasheet, we must short DP to DM on CH224D to use PD-only mode.

CH224D pin 18- NC (Not Connected in datasheet)

Internal Switch Configuration:

CH224D pin 5 (GATE)- Drives internal NMOS gate (no external connection)CH224D pin 6 (NMOS#)→GND(enables internal switch mode, disables external MOSFET control)

Current Sensing Configuration:

CH224D pin 14 (ISP)↔pin 15 (ISN)- Shorted together →GND- Not using current sensing feature (CH224D provides overcurrent protection internally)

Component Values

Input Capacitors

| Reference | Value | Type | Voltage | Package | Part Number | Purpose |

|---|---|---|---|---|---|---|

| C1 | 10µF | Electrolytic | 25V | - | - | VBUS bulk filtering (farther from IC) |

| C2 | 100nF | Ceramic X7R | 25V | 0603 | - | VBUS high-freq decoupling (CLOSE to IC) |

VDD Decoupling Capacitor

| Reference | Value | Type | Voltage | Package | Part Number | Purpose |

|---|---|---|---|---|---|---|

| C30 | 1µF | Ceramic X5R | 16V | 0603 | C6119849 | VDD internal regulator decoupling (close to pin 7) |

Configuration Resistor

| Reference | Value | Tolerance | Package | Part Number | Purpose |

|---|---|---|---|---|---|

| R11 (Rset) | 56kΩ | ±0.1% | 0603 | C705785 | 15V voltage configuration |

CC Pull-down Resistors (CRITICAL!)

| Reference | Value | Tolerance | Package | Part Number | Purpose |

|---|---|---|---|---|---|

| R12, R13 | 5.1kΩ | ±1% | 0603 | C23186 | USB-PD sink identification (Rd pull-downs on CC1, CC2) |

CRITICAL: R12 and R13 are REQUIRED for USB-PD operation! Without these 5.1kΩ pull-downs on CC1 and CC2, the PD adapter will not recognize the device as a sink and PD negotiation will fail.

Note on Status Indication: CH224D does not have a Power Good (PG) output pin. Power supply status is indicated by the output stage LEDs (LED2, LED3, LED4 on +12V, +5V, -12V rails) which confirm the entire power chain is operational.

Design Considerations

USB-C PD Negotiation Process

The CH224D follows this sequence:

- Initial Connection (0-100ms):

- USB-C connector makes physical contact

- VBUS initially at 5V (default USB power)

- CH224D detects CC1/CC2 orientation via 5.1kΩ pull-down resistors

- Critical: Without R12/R13 pull-downs, PD adapter won't recognize device as sink!

- Capability Discovery (100-200ms):

- CH224D requests available voltages via CC communication

- PD Adapter responds: 5V, 9V, 12V, 15V, 20V profiles

- Voltage Request (200-300ms):

- CH224D requests 15V (based on R11 = 56kΩ configuration)

- Reads CFG1 voltage to determine which voltage to request

- Acceptance & Voltage Transition (300-1000ms):

- PD Adapter accepts request

- VBUS transitions: 5V → 15V on the SAME pin (pin 2)!

- CH224D internal switch passes negotiated voltage through

- Power Ready (>1000ms):

- VBUS stable at 15V

- System can draw up to 45W (15V × 3A)

- Power supply ready for use

Configuration Resistor Selection

Critical: Rset must be a precision resistor (±0.1% or better) to ensure correct voltage selection.

- 56kΩ ±0.1%: Selects 15V reliably

- Other tolerances: May cause incorrect voltage negotiation or selection failure

- Part: RT0603BRD0756KL (JLCPCB C705785)

Layout Recommendations

- VBUS Input Caps: Place C1 and C2 as close as possible to pin 2 (VBUS)

- VDD Decoupling: Place C30 ceramic capacitor very close to pin 7 (VDD)

- Ground Plane: Connect EPAD (pin 0) to ground plane with multiple vias

- Thermal: EPAD provides thermal dissipation - use solid ground connection

- CC Lines: Keep CC1/CC2 traces away from switching noise sources

- Rset Placement: Place R2 (Rset) close to DRV/CFG1 junction for clean analog signal

Troubleshooting

| Symptom | Possible Cause | Solution |

|---|---|---|

| No PD negotiation at all | Missing CC pull-downs R12, R13 | CRITICAL: Add 5.1kΩ resistors on CC1, CC2 to GND! |

| No PD negotiation | NMOS# not tied to GND | Verify pin 6 (NMOS#) connected to GND |

| No PD negotiation | DP-DM not shorted | Short pins 8 (DP) and 9 (DM) together for 6-pin connector |

| No 15V output | Rset value incorrect | Verify R11 = 56kΩ ±0.1% |

| No 15V output | CFG1/DRV/Rset topology wrong | Check: DRV-CFG1 junction, then Rset to GND (NOT from VBUS!) |

| Stuck at 5V | PD adapter doesn't support 15V | Try different PD adapter with 15V capability |

| Intermittent negotiation | Inadequate VBUS capacitance | Check C1 (10µF bulk), C2 (100nF ceramic) placement |

| Overheating | Poor thermal connection | Improve EPAD ground connection with multiple vias |

| Wrong CC orientation detection | Incorrect CC1/CC2 pin assignment | Verify CC1=pin 11, CC2=pin 10 (not reversed!) |